Il Politecnico di Milano sviluppa un chip che accelera l’elaborazione dei dati e riduce i consumi energetici

Il Politecnico di Milano ha sviluppato un chip innovativo capace di accelerare l’elaborazione dei dati e ridurre drasticamente i consumi energetici.

Basato sull’approccio Closed-Loop In-Memory Computing, il dispositivo segna un progresso concreto verso sistemi di calcolo più efficienti e sostenibili. Pubblicato su Nature Electronics, il lavoro evidenzia la fattibilità industriale del calcolo analogico in memoria.

Una svolta per il computing: riduzione dei consumi e aumento della velocità

Il Dipartimento di Elettronica, Informazione e Bioingegneria (DEIB) del Politecnico di Milano ha annunciato la realizzazione di un chip che introduce un approccio radicalmente diverso al calcolo computazionale: il Closed-Loop In-Memory Computing (CL-IMC). Il progetto, guidato dal prof. Daniele Ielmini e descritto su *Nature Electronics*, è il risultato di anni di ricerca condotti nell’ambito del programma europeo ANIMATE, finanziato tramite un ERC Advanced Grant nel 2022.

L’obiettivo era superare le inefficienze strutturali dell’architettura von Neumann, in cui dati e istruzioni devono continuamente essere trasferiti tra memoria e processore. Questo meccanismo comporta un costo energetico elevato e introduce latenze rilevanti nei sistemi convenzionali, ostacolando la scalabilità verso applicazioni sempre più complesse come intelligenza artificiale, robotica e comunicazioni avanzate.

Il principio del Closed-Loop In-Memory Computing

Il concetto alla base del CL-IMC si fonda sull’elaborazione dei dati direttamente dove questi sono memorizzati. Invece di spostare continuamente le informazioni verso l’unità di calcolo, come avviene nei sistemi digitali classici, il chip realizza i calcoli direttamente all’interno della memoria. Questo elimina una delle principali inefficienze energetiche dell’informatica tradizionale.

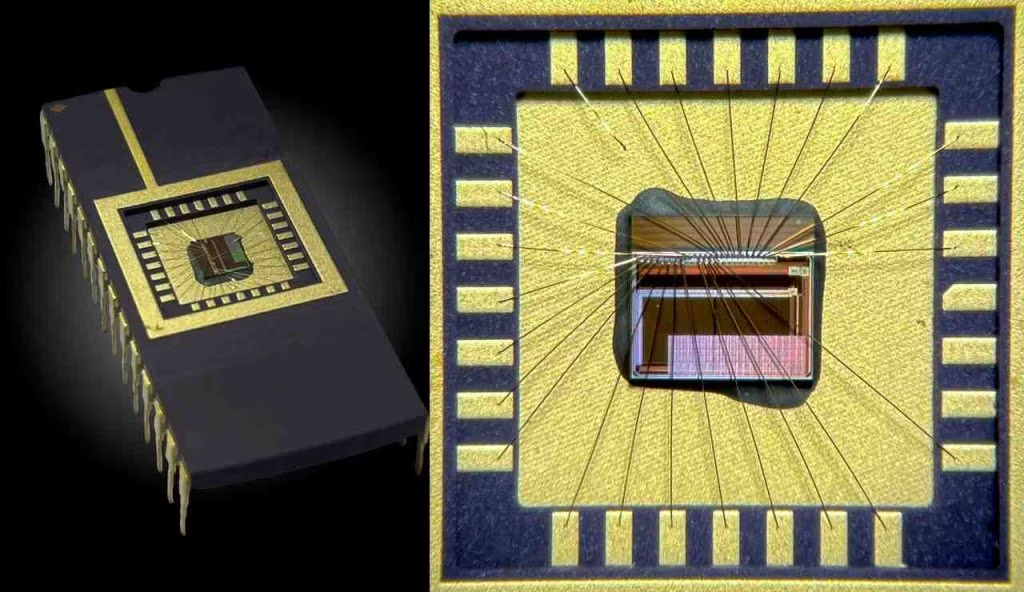

Nel caso specifico, l’approccio è reso possibile da una combinazione di circuiti analogici e celle di memoria resistiva programmabile. Il chip realizzato dai ricercatori del Politecnico impiega array 64×64 di queste memorie, integrate con componenti aggiuntivi come celle SRAM, resistori e convertitori analogico-digitali, in un’architettura completamente basata su tecnologia CMOS.

Architettura tecnica del chip: componenti e innovazioni

Il dispositivo sviluppato è un acceleratore analogico integrato, progettato per operare su scala di chip e dimostrare la scalabilità industriale del concetto. I suoi elementi chiave includono:

- Array 64×64 di memorie resistive (RRAM): utilizzate per la memorizzazione e l’elaborazione dei dati

- Componenti CMOS standard: compatibilità con i processi di produzione esistenti

- Amplificatori operazionali e ADC: per la gestione dei segnali analogici e la conversione verso domini digitali

- Celle SRAM e resistori integrati: per supportare funzioni di controllo e ottimizzazione del flusso dati

L’integrazione di questi componenti su un unico chip consente di eseguire operazioni complesse direttamente in memoria, evitando il passaggio attraverso un processore centrale. Questo permette una significativa riduzione della latenza computazionale e un miglioramento nella densità energetica, due aspetti fondamentali per le applicazioni edge e ad alte prestazioni.

Risultati sperimentali: accuratezza e prestazioni

Nei test sperimentali, il chip ha mostrato un’accuratezza di calcolo comparabile con quella dei sistemi digitali convenzionali, pur utilizzando segnali analogici. Si tratta di un risultato rilevante, poiché il calcolo analogico è spesso associato a difficoltà nella precisione.

Parallelamente, i dati raccolti evidenziano:

- Riduzione dei consumi energetici rispetto agli approcci tradizionali

- Minore latenza nelle operazioni di calcolo

- Occupazione ridotta di superficie sul silicio, con vantaggi in termini di costi e scalabilità

Il chip si configura quindi come una piattaforma concreta per applicazioni reali, con la possibilità di essere adattato a contesti ad alta intensità computazionale, mantenendo efficienza e compattezza.

Collaborazioni internazionali e sviluppo del progetto ANIMATE

Il risultato è parte del progetto ANIMATE, il cui obiettivo è sviluppare una catena tecnologica completa: dal dispositivo fisico alle architetture di sistema, passando per l’integrazione circuitale e la validazione su applicazioni specifiche. Il progetto ha coinvolto un team multidisciplinare e internazionale, con il contributo anche della Peking University e la partecipazione di dottorandi, studenti e ricercatori senior.

Piergiulio Mannocci, primo autore della pubblicazione, ha sottolineato come l’infrastruttura sviluppata dimostri il potenziale del CL-IMC in scenari ad alta efficienza energetica. L’approccio integra conoscenze avanzate di fisica dei dispositivi, progettazione di circuiti integrati e algoritmi di controllo, in una piattaforma unificata che rende il sistema facilmente traslabile su larga scala.

Applicazioni potenziali del calcolo in-memoria analogico

Le implicazioni di questa tecnologia sono rilevanti in più settori dell’informatica e dell’ingegneria. Tra le applicazioni più dirette:

Intelligenza artificiale: le reti neurali, soprattutto in fase di inferenza, beneficiano in modo diretto della riduzione della latenza e dei consumi, con un notevole vantaggio nei dispositivi edge.

Data center e cloud computing: la possibilità di ridurre i costi energetici per l’elaborazione di grandi moli di dati rappresenta un vantaggio economico e ambientale.

Robotica e automazione: i sistemi autonomi richiedono elaborazioni in tempo reale che il CL-IMC può fornire con maggiore efficienza.

Telecomunicazioni avanzate e 6G: l’evoluzione verso reti di nuova generazione prevede un incremento sostanziale del traffico dati, che richiederà architetture di calcolo più compatte e performanti.

Prospettive di trasferimento industriale e prossimi sviluppi

Secondo quanto dichiarato dal prof. Daniele Ielmini, il chip sviluppato dimostra la fattibilità su scala industriale del calcolo analogico in memoria. L’obiettivo nei prossimi anni sarà trasferire questa tecnologia in ambiti produttivi concreti, collaborando con aziende e partner tecnologici per integrare il CL-IMC in dispositivi commerciali.

Il gruppo di ricerca del DEIB è attualmente al lavoro su nuovi prototipi e su algoritmi ottimizzati per sfruttare al meglio l’architettura analogica. L’interesse di potenziali investitori e partner industriali è già stato manifestato, in vista di una futura industrializzazione della tecnologia.

Un nuovo paradigma architetturale per l’hardware del futuro

La realizzazione del chip CL-IMC rappresenta un esempio di trasformazione concreta nel design dei sistemi di calcolo. Superando la separazione funzionale tra memoria e logica computazionale, si apre una prospettiva in cui l’elaborazione può avvenire in prossimità del dato, riducendo colli di bottiglia e aumentando l’efficienza complessiva del sistema.

Questo paradigma architetturale non sostituisce i modelli esistenti, ma li integra e li rafforza, offrendo soluzioni mirate per scenari specifici ad alta densità di calcolo. L’approccio sviluppato al Politecnico di Milano dimostra la maturità tecnologica di soluzioni in-memory analogiche e ne evidenzia l’applicabilità in ambienti reali.